软件星级:3分

软件星级:3分

加速高层次设计

软件定义 IP 生成 - Vivado 高层次综合 (HLS)

基于模块的 IP 和 Vivado IP 集成

基于模型的 DSP 设计和 System Generator for DSP集成

加速验证

Vivado 逻辑仿真器

集成混合语言仿真器

集成 & 独立 编程与调试环境

加速验证超过 100 倍,通过 C、 C++ 或 SystemC 以及 Vivado HLS

加速实现

设计实现时间缩短 4 倍

设计密度提升 20%

在低端 & 中档产品中实现高达 3 速度级性能优势,在高端产品中实现 35% 功耗优势

在过去四年中,赛灵思的前沿客户已经开创和成熟了现在包含在HLx版本中的启用C和IP设计技术和方法,并证明了10-15X的生产力潜力。为了实现这种生产力,这些客户采用了以下所有或一个子集;

- 基于C的设计和优化的重用,

- IP子系统的重用,

- 集成自动化,加快设计关闭。

不同于传统的基于RTL的设计,大部分设计工作都花在设计过程的后端,基于C和IP的设计可以极大地优化设计重用,以加快创建速度,快速设计探索更好的微架构,替代错误手动C到RTL转换,在集成基于C和RTL的IP时消除了时间和错误,并大大缩短了验证时间。客户利用高层次的抽象,发现他们可以快速得到整体的更好或更好的结果质量(性能,功率,利用率)。

为了实现这些高效率流程,HLx版本包括Vivado HLS,Vivado IPI,LogicCORE IP子系统和完整的Vivado实现工具套件。此外,赛灵思及其联盟生态系统正在不断扩大市场特定的C库,例如用于视频和图像处理的OpenCV以及汽车驾驶员辅助系统(ADAS)和数据中心应用的机器学习。赛灵思新的LogiCORE IP子系统是高度可配置的,市场定制的构建块,可集成多达80个独立的IP内核,软件驱动程序,设计示例和测试台。新的IP子系统可用于以太网,PCIe,视频处理,图像传感器处理和OTN开发。这些IP子系统基于行业标准,如AMBA AXI 4互连协议,IEEE P1735加密和IP-XACT,以实现与赛灵思和联盟成员IP的互操作性,并加速集成。

基于C的IP和预先封装的IP子系统的结合,迅速结合使用Vivado IP Integrator进行集成自动化。 Vivado IPI的集成自动化提供了一个设备和平台意识的交互式环境,支持关键IP接口的智能自动连接,一键式IP子系统生成,实时DRC和接口更改传播,以及强大的调试功能。平台感知智能,可以使用正确的外设,驱动程序和内存映像来预配置Zynq SoC和MPSoC处理系统,以支持目标板。设计团队现在可以快速识别,重用和集成软件和硬件IP,面向ARM处理系统和高性能FPGA逻辑。

HLx完成SDx用于创建和部署平台

HLx加速了硬件工程师的所有可编程平台的创建,修改和编程,补充了针对软件和系统工程师量身定制的Xilinx SDx开发环境(SDSoC,SDAccel和SDNet)。 SDx系列开发环境支持使用C,C ++,OpenCL和新兴的P4语言进行数据包处理的HLx生成平台的软件定义编程。 HLx和SDx代表赛灵思新一代设计支持解决方案,用于开发更智能,连接和差异化的系统,利用所有可编程器件(包括Zynq SoC,MPSoC,ASIC级FPGA和3D IC)的新纪元。

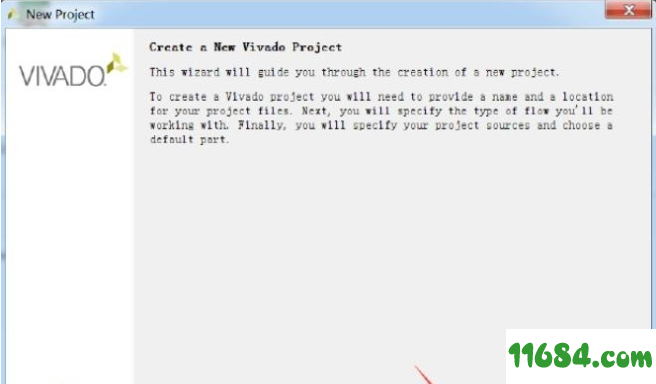

首先使用vivado搭建一个底层硬件系统,具体操作过程如下,用图的方式来说明,直观方便

打开vivado

单击create new project,如下图,单击next

继续单击next,如下

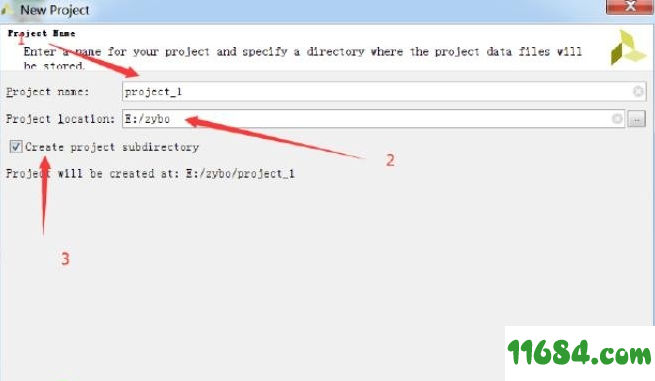

解释一下

1:工程的名字

2:工程在电脑中的位置,不要中文,不要空格

3:打上勾表示在2的位置基础上创建一个子目录,不勾就表示不创建,我一般都是按大类来分,比如米尔的文件夹,zingsk的文件夹,zybo的文件夹,所以我都勾上,我的位置如下图

设置好了之后继续单击next,这里是说创建一个什么样的工程

Xilinx Vivado Design Suite 2016.4

一般都是rtl的工程,其他的我还没研究过,直接看官方文档学的,做fpga或者soc,sopc,都是rtl工程。这里也有个可以勾选的地方,勾上的意思是现在不指定源文件,如果不够上,就进入具体设置,有硬件语言的类型,ip的选择,and so on ,可以自己去看看,建议勾选,这些可以在工程中设置的,没有必要提前设置

单击next

Xilinx Vivado Design Suite 2016.4

里面可选的就很多了,从上到下,从左到右简单的说下 Part和board分别指的是单个芯片和官方或者安富利的板子

下面的这些是指fpga的类和速度和温度,左后的search,是你之前用过的芯片的记录或者直接收你想要的芯片名字,第一次选好,以后直接到search中选就行

Xilinx Vivado Design Suite 2016.4

这个是zybo的板子的芯片型号,或者在board中直接选zybo,继续单击next,一个summary

Xilinx Vivado Design Suite 2016.4

继续单击next,vivado给咱们创建工程

Xilinx Vivado Design Suite 2016.4

创建好了就是这个样子,一个空的工程

Xilinx Vivado Design Suite 2016.4

接下来我们要建立一个空的图片,用来搭建zynq的底层,单击箭头指的地方

这个表示设计的名字和存储的路径,一般都是系统,我习惯于功能加系统的方式命名,比如这次是对gpio进行操作,我会做gpio_sys,然后单击ok

Xilinx Vivado Design Suite 2016.4

具体的大家可以查看压缩包的地址